Articles

- Intel

- Samsung

- Texas Instruments

- STMicroelectronics

- Infineon

- NXP Semiconductors

- Microchip

- Analog Devices

- onsemi

- Skyworks Solutions

- Avago

- Marvell

- Omnivision Technologies

- ROHM

- Seoul Semiconductor

- Silego

- Cirrus Logic

- Silicon Labs

- Lattice Semiconductor

- Cypress Semiconductor

- Toshiba

- Mitsubishi

- Panasonic

- Sharp

- Omnetics

- Laird

- TDK-Lambda

- WAGO

- All Distributors

An Introduction to RISC-V—Understanding RISC’s Open ISA

RISC-V is an open instruction set architecture (ISA) that has gained significant traction as a viable alternative to proprietary architectures such as ARM. Since its inception, RISC-V has steadily increased in popularity in both academic and commercial sectors.

Understanding RISC vs. CISC

RISC, which stands for Reduced Instruction Set Computer, is a computer architecture philosophy that emerged in the 1980s as a response to the Complex Instruction Set Computer (CISC) models prevalent at the time, such as those from Intel and Motorola. Initially, CISC architectures utilized dense instruction sets designed to support a wide range of operations considered useful. However, research teams, including those from IBM and UC Berkeley, discovered that compilers typically used only a small subset of these complex instructions. This insight led to a re-evaluation of the need for expansive instruction sets, emphasizing simplicity to enhance efficiency.

RISC is fundamentally different from CISC in several ways. Typically, CISC CPUs possess a limited number of registers while offering a plethora of instructions, most of which can access memory directly. In contrast, RISC CPUs feature a greater number of registers and a more modest instruction set, with memory access primarily restricted to a few load and store instructions.

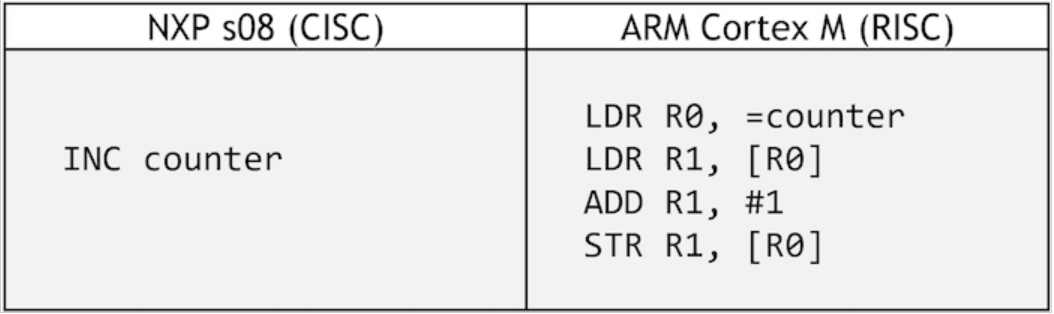

To illustrate this difference, consider Table 1, which compares code for incrementing a counter variable using a CISC CPU (the NXP s08) and a RISC CPU (the ARM Cortex M0+). In this comparison, the CISC architecture allows for incrementing a variable in a single instruction, whereas the RISC architecture requires accessing memory through load and store operations. While this highlights a difference in code size, it's important to note that this is not a direct comparison of technical superiority, as the architectures have inherent differences.

Table 1. An example comparison between CISC and RISC codes.

Today, the Intel x86/x64 architecture exemplifies that CISC microprocessors have not been entirely displaced by RISC, while the ARM architecture demonstrates RISC's dominance in the mobile device market.

History of RISC-V

The acronym RISC was coined around 1980 by Professor David Patterson at UC Berkeley, whose collaborative work with Professor John Hennessy at Stanford University resulted in landmark texts such as “Computer Organization and Design” and “Computer Architecture: A Quantitative Approach.” Their contributions to RISC architecture earned them the ACM A.M. Turing Award in 2017.

Fast forward to 2010, the development of the fifth generation of RISC research culminated in what is now known as RISC-V (pronounced "risk-five"). This initiative represents a significant advancement in open computing architectures.

RISC-V International: An Open ISA

RISC-V is characterized as an open instruction set architecture, meaning that developers can implement a RISC-V CPU in a microprocessor or microcontroller without the obligation to pay royalties. RISC-V International is a global nonprofit organization responsible for owning and maintaining the intellectual property of the RISC-V ISA. One of its primary goals is to ensure that RISC-V's design prioritizes simplicity and performance over commercial interests. This objective is supported by its members, which range from individual developers to major organizations such as Google, Intel, and Nvidia. Membership offers numerous benefits, including opportunities to contribute to ISA design and to vote on proposed changes.

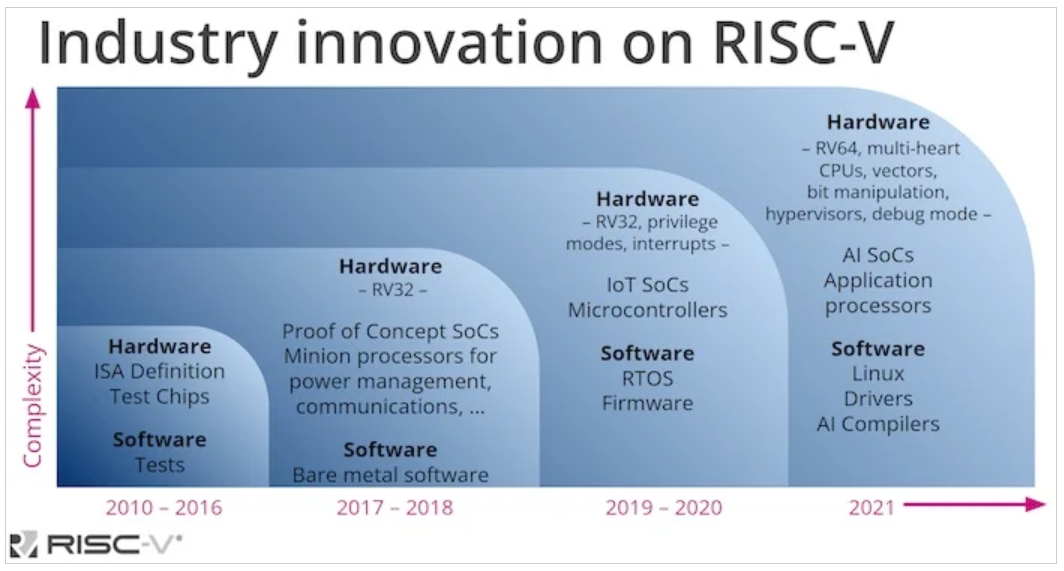

Figure 1 illustrates a high-level timeline of RISC-V's development, showing its increasing acceptance in the microprocessor industry and its steady growth in both hardware and software adoption since its inception.

Figure 1. Since its inception in 2010, RISC-V has been well received by the microprocessor industry, and adoption has been steadily growing both in hardware and software.

RISC-V ISA Conventions and Extensions

As the fifth generation of a long-standing research project, RISC-V aims to learn from past architectural shortcomings. It is designed as a modular ISA rather than a traditional incremental ISA, allowing implementations to consist of a mandatory base ISA and a variety of extensions. This modularity enables the customization of CPUs to meet specific application needs.

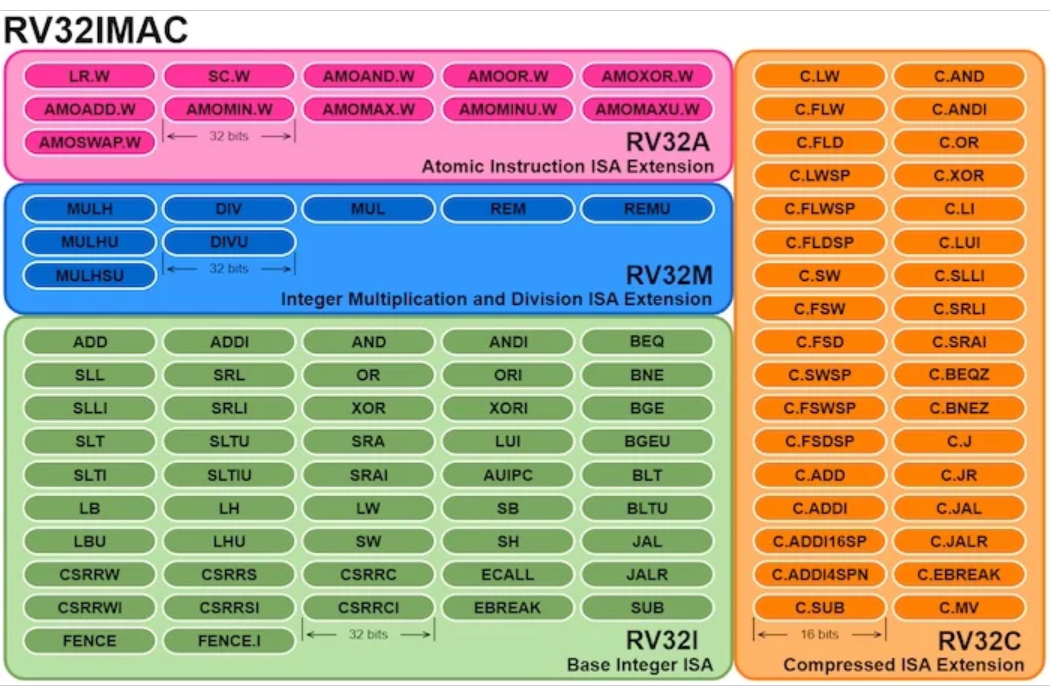

The naming convention for custom ISAs begins with "RV" (for RISC-V), followed by the bit width and an identifier for the variant. For example, RV32IMAC indicates:

· RV32I: A 32-bit CPU with the Base Integer ISA

· M: The Integer Multiplication and Division extension

· A: The Atomic Instruction extension

· C: The Compressed Instruction extension

Figure 2. The instruction set for the RV32IMAC ISA shows the modular (not incremental) nature of RISC-V. A mandatory Base ISA is combined with a set of extensions [click to enlarge].

Figure 2 demonstrates the modular nature of RISC-V, showing how the mandatory base ISA is complemented by various extensions. Compilers are aware of the included extensions in the target CPU, allowing them to generate optimized code. If the code includes instructions from missing extensions, the hardware can trap and execute alternative software functions from the standard library.

Base Integer ISA

The RV32I base integer ISA is a streamlined set of 47 instructions that implement essential operations for basic functionality with 32-bit integers (with a 64-bit counterpart known as RV64I). This ISA, encoded in 32 bits, includes instructions for:

· Addition

· Subtraction

· Bitwise operations

· Load and store

· Jumps

· Branches

The base ISA also specifies 32 CPU registers, each 32 bits wide, in addition to the program counter. The special register x0 always reads as zero, following a convention established in earlier RISC ISAs. While all registers are available for general use, the application binary interface (ABI) designates specific purposes for each, such as holding temporary or saved data, pointers, and return addresses.

RISC-V Multiplication and Floating Point

The RV32M extension provides eight instructions for performing multiplication and division on integers, with the RV64M extension adding five more instructions for the 64-bit variant. The RV32F extension introduces 32 separate registers for 32-bit floating-point numbers along with 26 floating-point instructions, while the RV32D extension supports 64-bit floating-point numbers with 32 registers and double-precision operations.

RISC-V Compressed Instructions

The RV32C extension adds a clever feature by offering an alternative 16-bit encoding for a select subset of existing instructions. After analyzing extensive lines of code generated by modern optimizing compilers, the RISC-V creators identified the most frequently used instructions and developed 16-bit versions, trading off some functionality of their 32-bit counterparts, which remain available in the RV32I base ISA.

This compression is feasible due to the following observations:

1. Certain registers are used more often than others.

2. One operand is typically overwritten.

3. Some immediate values are favored.

By compressing the most commonly used instructions, RISC-V enhances the potential for significant program size reduction.

Other RISC-V Extensions

Numerous additional extensions provide modern microprocessors with an array of functionalities, including:

· Embedded Base ISA (RV32E)

· Extensions for Atomic Operations (A)

· Bit Manipulation (B)

· Vector Operations (V)

· And many more.

RISC-V Implementation

A variety of companies are now manufacturing different variants of RISC-V cores for their microcontrollers, microprocessors, and System on Chips (SoCs). SiFive, for instance, was the first company to produce silicon based on the RISC-V ISA, offering a range of products from low-end microcontrollers to high-performance SoCs.

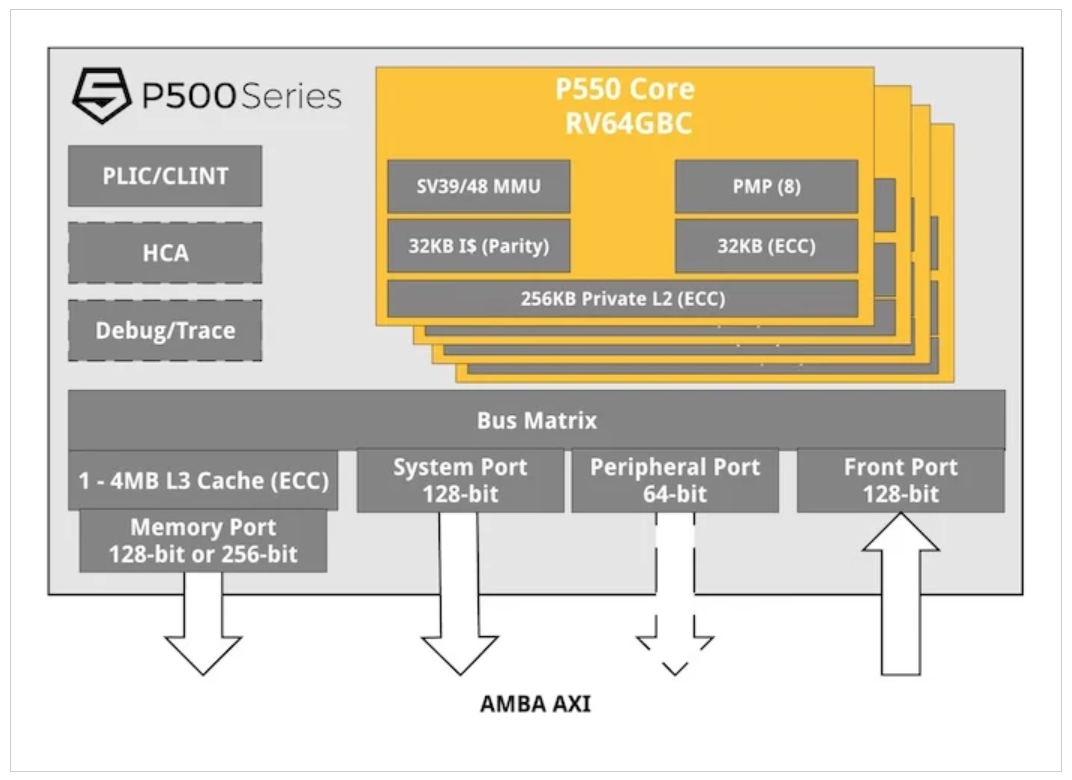

Figure 3 presents an example of a RISC-V block diagram, specifically showcasing the architecture of the P550 high-performance application processor.

The applications of RISC-V are not limited to integrated circuits. A multitude of projects are underway across various domains, including compilers, simulators, development environments, and operating systems. For a comprehensive list of these projects, you can visit the relevant GitHub repository.

In summary, RISC-V is a thrilling development in the realm of computer architecture, and now is an excellent time to engage with this innovative movement. For further information, consider visiting the RISC-V International website to learn more about the ongoing efforts and opportunities in this exciting field.